| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | News | Index |

.jpg) |

.jpg) |

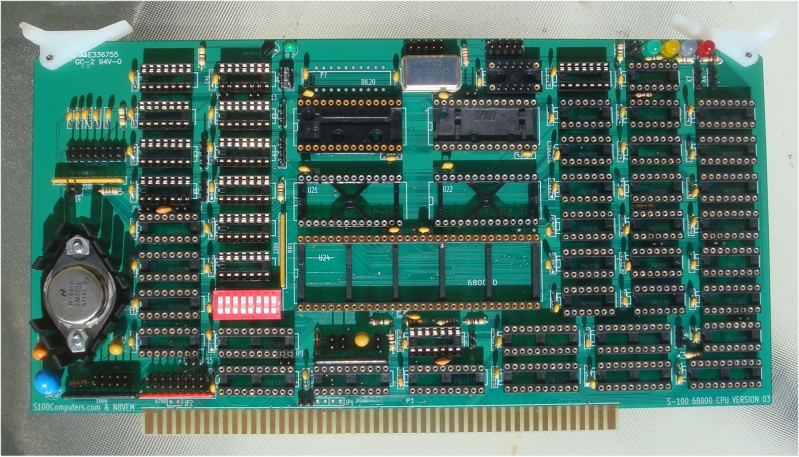

Now the one truly remarkable feature the 68K CPU S-100 board has going for it is the fact that back in 1987 a guy named Alan Wilcox wrote a whole book describing a complete S-100 based 68K CPU board. The book is the only one of its kind -- describing the construction of an S-100 CPU board, and goes into considerable detail chapter by chapter building up a completely functional board. The book is an absolute "must read" for anybody building a 68K system. The title is "68000 Microcomputer Systems Designing & Troubleshooting" by Alan D. Wilcox. Prentice-Hall Inc. Publishers, 1987. Copies can be obtained from time to time on eBay and Amazon. |

.jpg)

|

|

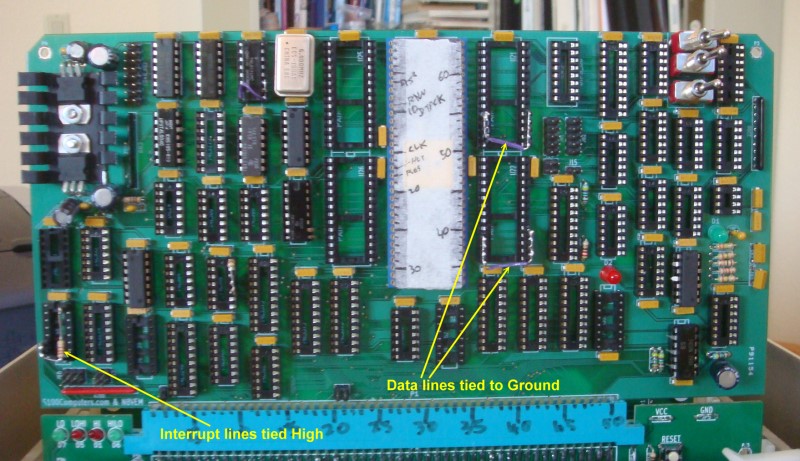

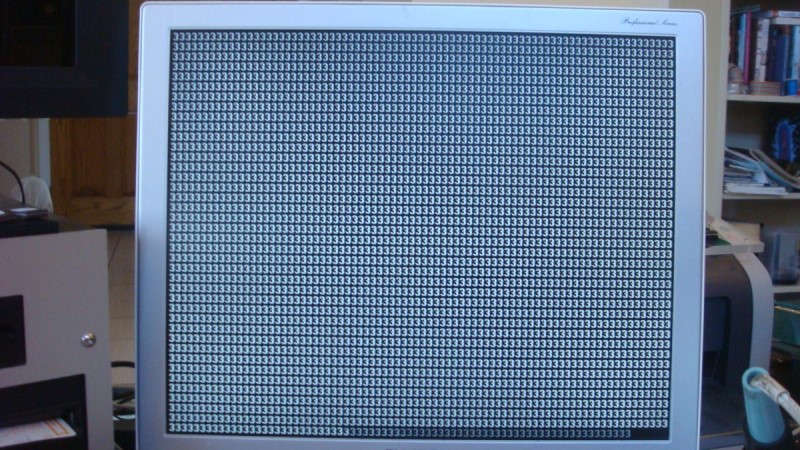

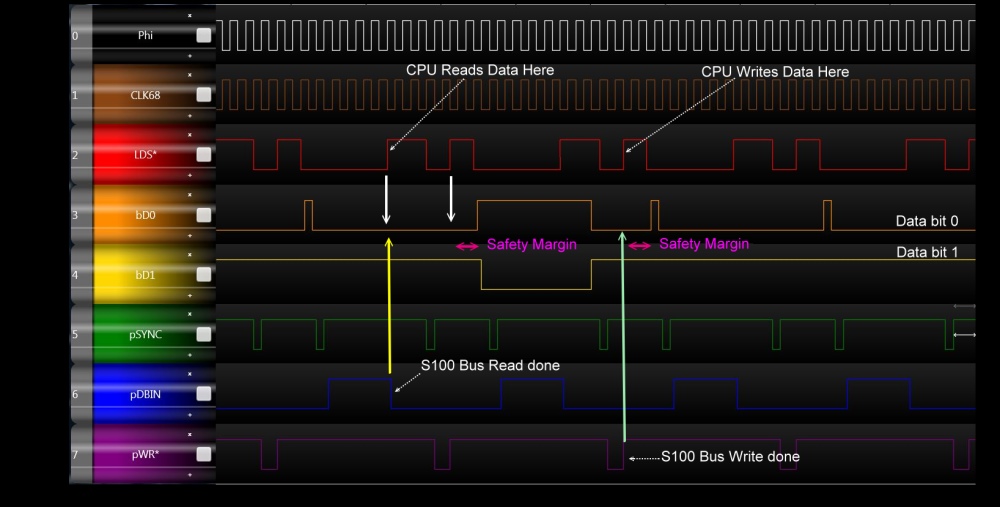

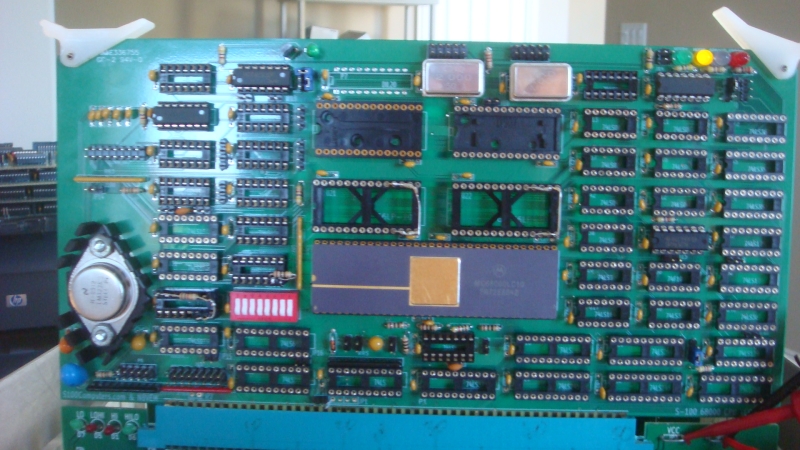

| 68000 CPU board in "Freerun" test mode | |

|

|

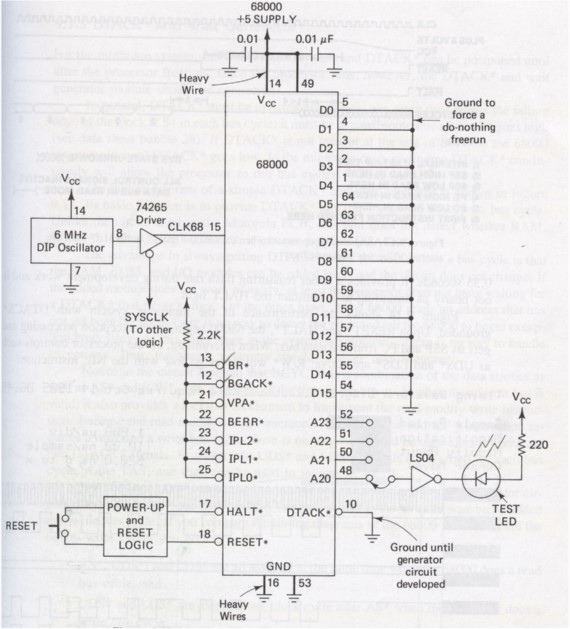

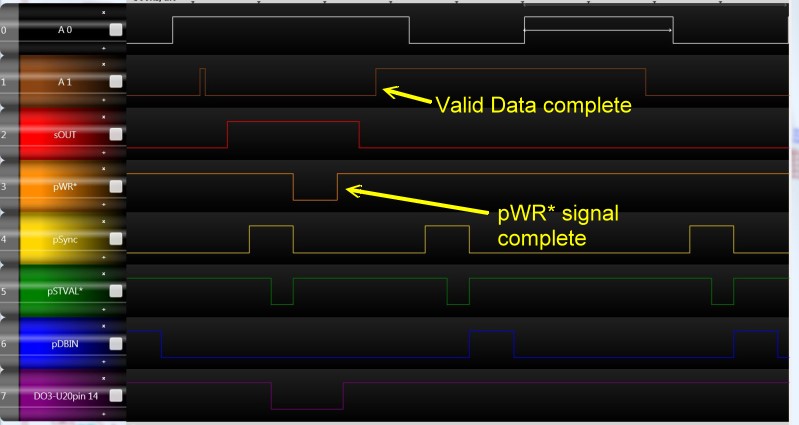

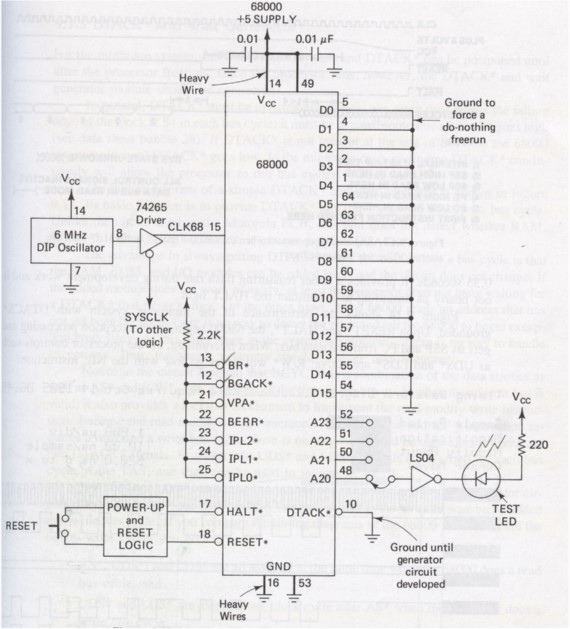

| Freerun test circuit |

|

|

|

|

|

|

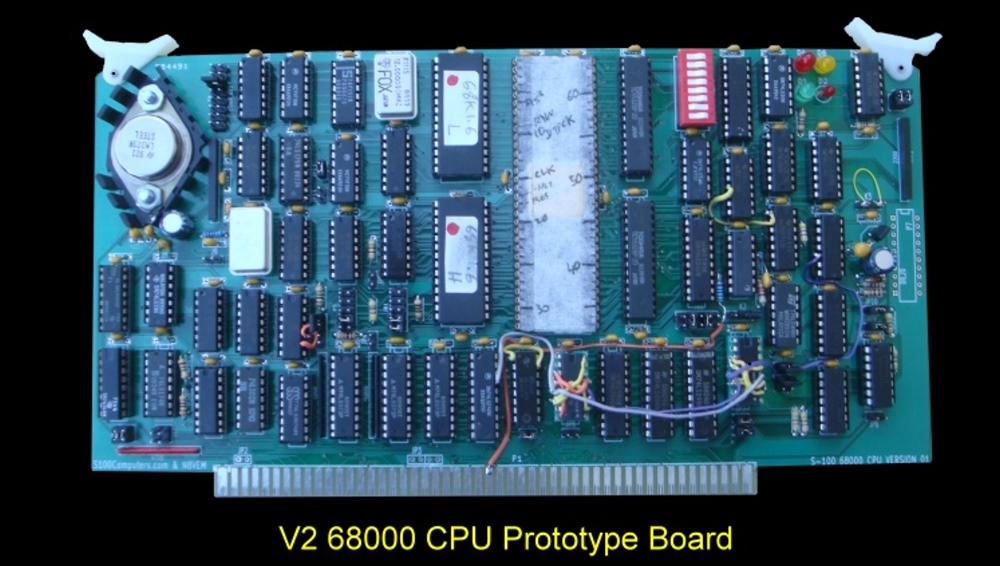

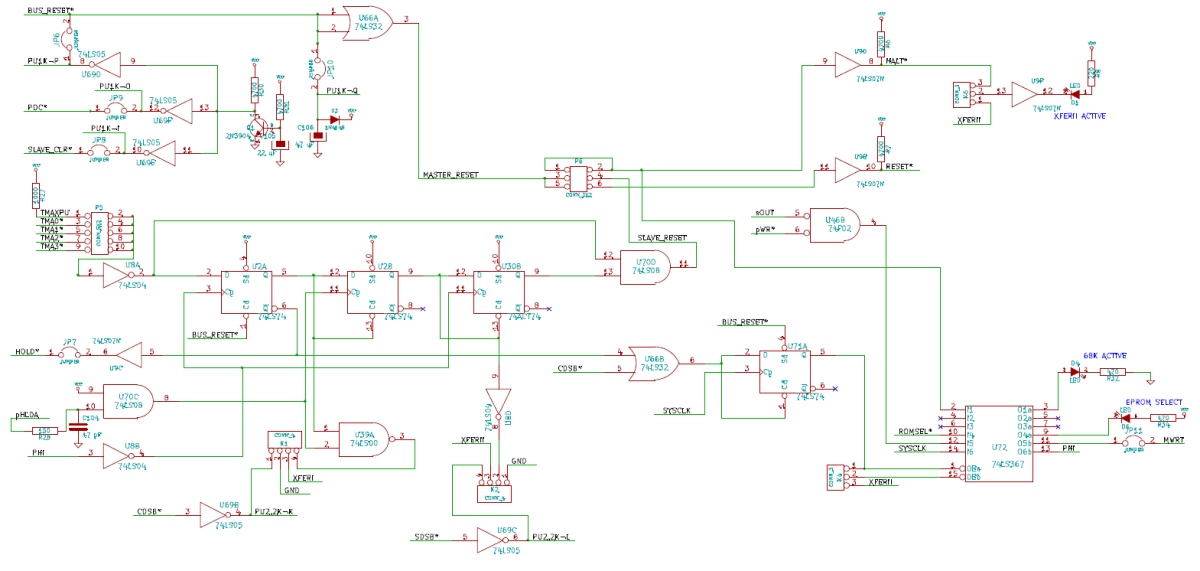

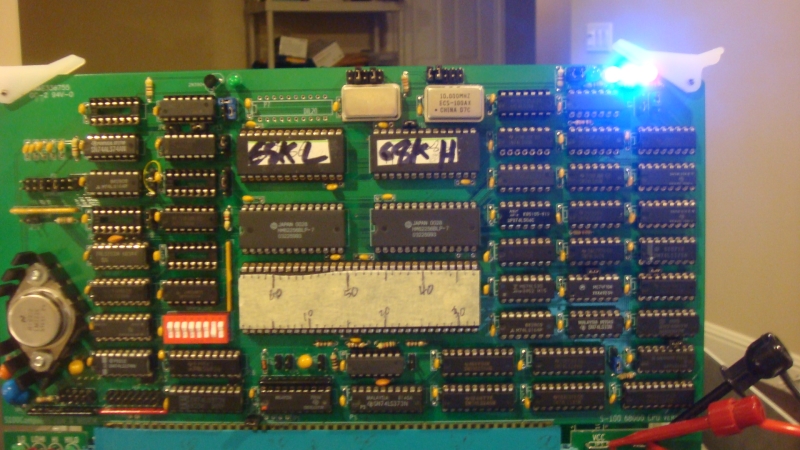

| Added switching/handshake circuit to allow S-100 bus Master - Slave bus switching | |

| Removed hardware switches and single step circuit. Stepping can be done with the SMB | |

| Selected use of 74Fxx chips for up to 7MHz S-100 Bus clock speeds | |

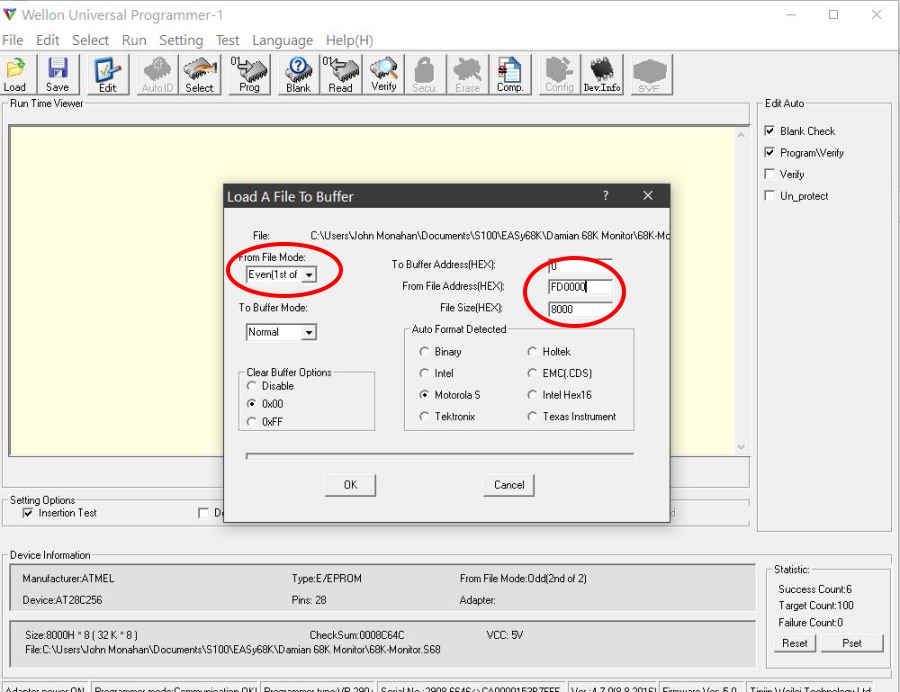

| The board can now utilize 28C256 (32KX8) EEPROMS | |

| More LED's to show what is going on. Board active, EPROM active, Supervise Mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

This page was last modified on 02/07/2024